原子層蒸着(ALD)は何十年も前から行われてきましたが、ALD高誘電率材料をロジック デバイスのゲート誘電体やDRAMのキャパシタ誘電体として統合する取り組みによって、研究コミュニティは技術の習得と使用範囲の拡大を図ってきました。

Veeco/CNT ALDシステムは、Al2O3、HfO2、Ta2O5、TiO2、およびZrO2などのさまざまな高誘電率誘導体材料の研究に使用されてきました。ALD技術の柔軟性により、AlTiO、HfSiOなど膜を組み合わせたり、AlON、HfON、およびZrONなどの膜に窒素を組み込んだりすることで、膜の特性を微調整できます。ALD高誘電率誘導体膜の特性には、大容量、低リーク電流、および高破壊電圧などがあるため、エレクトロニクス用途に適しています。

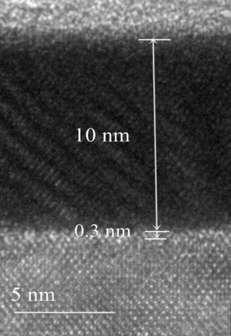

Fiji®に蒸着した窒化HfO2のHRTEM。L-T Huang, et al. “Improvement in electrical characteristics of HfO2 gate dielectrics treated by remote NH3 plasma,” Applied Surface Science Volume 266, 1 February 2013, Pages 89-93.

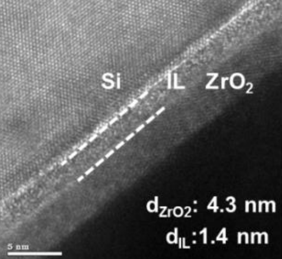

窒化Al2O3バッファ層にZrO2を蒸着したFiji®のHRTEM。J-J Huang, et al. “Improvement in Electrical Characteristics of Crystalline ZrO2 /Nitrided Al2O3 Gate Stacks Grown by Remote Plasma Atomic Layer Deposition,” ECS J. Solid State Sci. Technol. 2013 volume 2, issue 12, P524-P528

ZrO2/Al2O3スタックを蒸着したFiji®のHRTEM。A. O’Mahoney, et al. “Structural and Electrical Analysis of Thin Interface Control Layers of MgO or Al2O3 Deposited by Atomic Layer Deposition and Incorporated at the high-k/III-V Interface of MO2/InxGa1-xAs (M = Hf|Zr, x = 0|0.53) Gate Stacks,” ECS Transactions, 33 (2) 69-82 (2010).

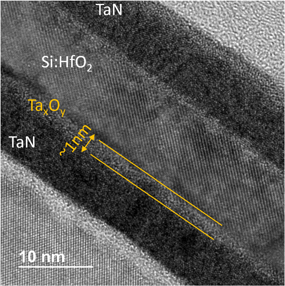

Si:HfO2膜を蒸着したFiji®のHRTEM。P.D. Lomenzo, et al. “TaN interface properties and electric field cycling effects on ferroelectric Si-doped HfO2 thin films,” Journal of Applied Physics 117, 134105 (2015).

主要なロジックおよびメモリ チップ メーカーが高誘電率ALD膜を製品に組み込んだことにより、ALD技術は製造工場で受け入れられ、ALD膜が性能とコストにおいて破壊的なメリットをもたらすことが期待される他のデバイス領域での模索が行われました。

電極

デバイス電極の材料には、適切な特性が必要です。低抵抗は一番の関心事ですが、適切な仕事関数や他のデバイス材料との化学的適合性などの他の膜特性も重要です。ALDは、さまざまな純金属(Pt、Ru、Ni)、金属窒化物(TiN)、および伝導性酸化物(RuO2)を製造できます。これらはすべて、エレクトロニクス用途における電極材料として研究されてきました。

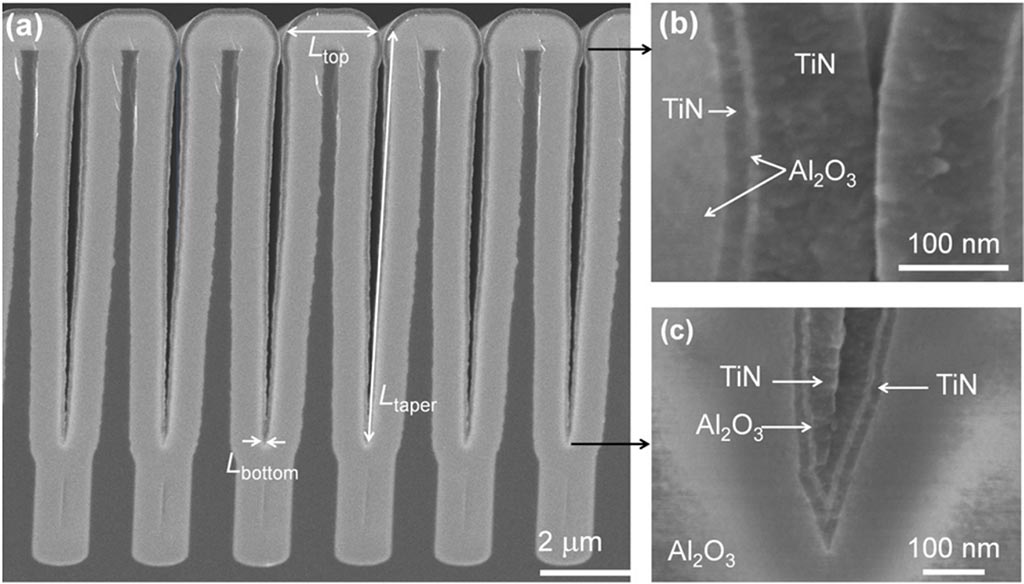

TiN-Al2O3-TiNトレンチ キャパシタを蒸着したFiji®の断面SEM画像。M. Burke, et al. “High aspect ratio iridescent three-dimensional metal–insulator–metal capacitors using atomic layer deposition,” J. Vac. Sci. Technol. A 33(1), Jan/Feb 2015.

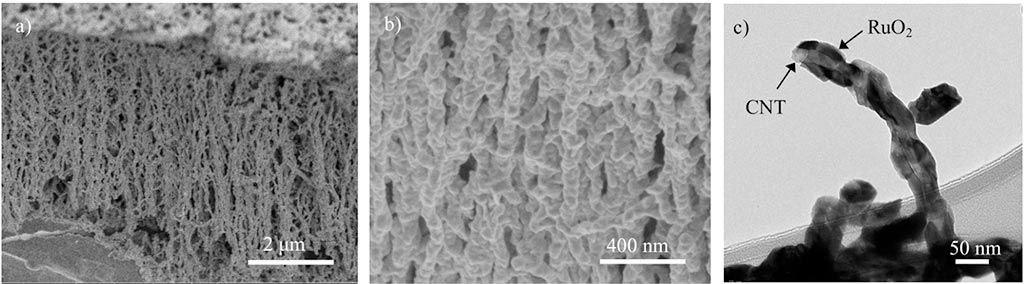

a) およびb) SEM images of Fiji® deposited RuO2でコーティングされたカーボンナノチューブを蒸着したFiji®のSEM画像 c) シングルRuO2でコーティングされたカーボン ナノチューブのTEM。R. Warren, et al. “ALD Ruthenium oxide-carbon nanotube electrodes for supercapacitor applications,” 2014 IEEE 27th International Conference on Micro Electro Mechanical Systems (MEMS).

バリア

現代の集積回路は、ナノスケールの多層配線スキームを利用して、半導体基板上の個別素子を相互接続し、有用な回路を生成し、電源配線を提供し、外部通信の入出力経路を提供しています。これらの相互接続は通常、パターン化された低誘電率層間絶縁膜(ILD)材料上に蒸着された細い銅線で、これによって接続経路をサポートおよび定義しています。銅は移動性の高い材料であり、ILDに直接蒸着すると誘電体に拡散し、デバイス性能は時間とともに低下します。

バリア膜は、銅蒸着の前にILD上に必ず蒸着されます。バリア膜が薄く導電性が高いほど、相互接続抵抗への全体的な影響は小さくなります。ALDは、非常に低い銅拡散特性を備えた、薄いコンフォーマルなピンホールのない、高伝導性の膜を蒸着する機能を備えたバリア用途に特に適しています。Veeco/Cambridge NanoTechシステムでは、数多くのALD窒化プロセスが開発されています。

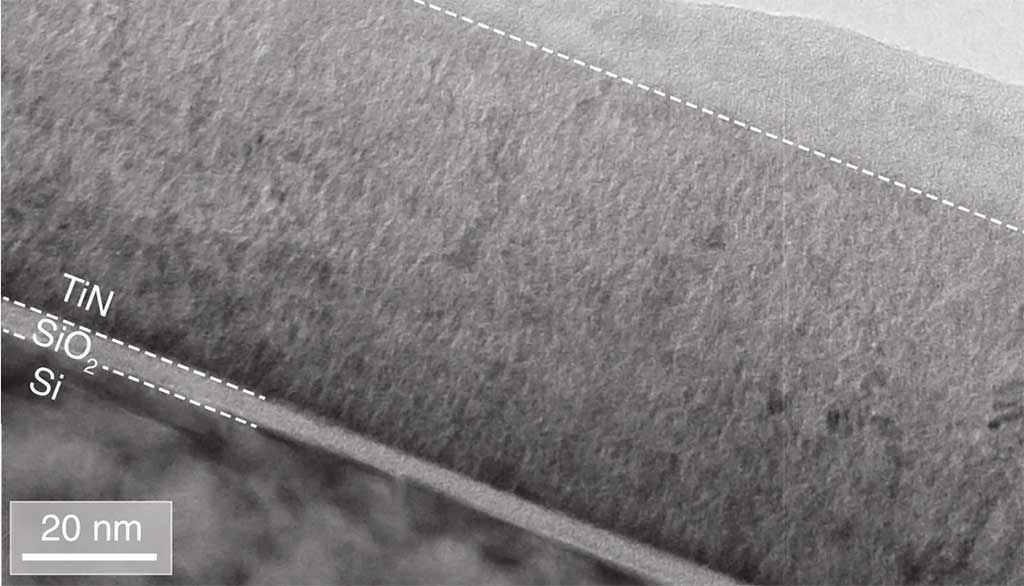

TiNを蒸着したFiji®のTEM画像。L. Assaud, et al. “Highly-Conformal TiN Thin Films Grown by Thermal and Plasma-Enhanced Atomic Layer Deposition,” ECS Journal of Solid State Science and Technology, 3 (7) P253-P258 (2014).